Страница: 6/12

Схема устройства статического ОЗУ

Схема устройства статического ОЗУ

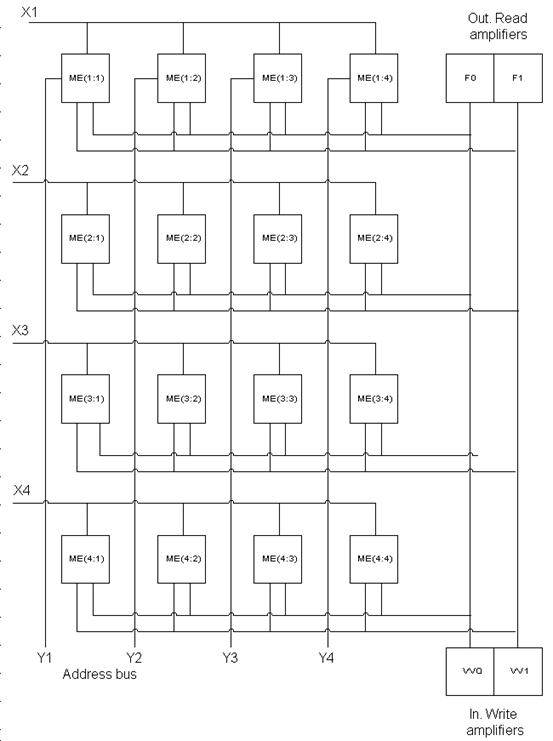

Для хранения четырехразрядного числа необходимо иметь 4 матрицы накопителя (понятное дело, что обычно используются восьмиразрядные числа, но описание его хранения слишком сложно для восприятия, хотя от четырехразрядного варианта отличается только лишь количеством элементов). Адресные входы матриц-накопителей соединяются параллельно и подключаются к дешифратору.

Схем включения блоков памяти

Схем включения блоков памяти

Так как матрица-накопитель одной рассматриваемой микросхемы содержит 16 элементов памяти, то при параллельном включении четырех таких микросхем получается запоминающее устройство, которое может одновременно хранить 16 четырехразрядных чисел (заметим в скобках, что современные устройства памяти оперируют 64-разрядными числами). Для адресации этих чисел необходимо иметь 16 различных адресных сигналов, что можно получить при четырехэлементном коде адреса. Например, при коде адреса 0000 сигналы единичного уровня появятся на шинах с номерами 1, которые на всех схемах выбирают элемента памяти с адресом 1.1. Таким образом, в первой схеме запишется 1й разряд числа, во второй – второй и т.д. Часть запоминающего устройства, предназначенная для хранения многоразрядного числа, называется ячейкой памяти.

Статическое ЗУ

Как уже отмечалось, в статическом ЗУ роль элемента памяти выполняет триггер. Возьмем матрицу из 16*16=256 элементов, т.е. организация накопителя будет 256*1 бит. Для обращения к такому ОЗУ необходимо подвести к нему сигнал,. разрешающий работу (ВМС – выборка микросхемы), к информационным входу и выходу, и восьмиразрядный код адреса к адресным входа дешифраторов.

Дешифратор управляет ключами выборки строк и столбцов, которые, в свою очередь вырабатывают сигналы, соединяющий выбранный элемент памяти и шину ввода-вывода. Сигналом запись-считывание (ЗС) устанавливается режим работы микросхемы.

При поступлении единичного уровня сигналов ЗС и ВМС открывается схема ввода информации. Через шину ввода-вывода и открытый ключ выборки столбца информация через вход поступает на выбранный элемент памяти.

При нулевом сигнале ЗС и сигнале ВМС открывается схема вывода информации на выход. При отсутствии сигналов ЗС и ВМС выход микросхемы отключается от внешней шины.

Схема работы статической памяти.

Схема работы статической памяти.

Динамическое ОЗУ

Динамическому ОЗУ нужна периодическая перезапись (регенерация) информации для ее хранения. Возьмем, например схему с емкостью 4096*1 бит с матрицей 64*64=4096 элементов памяти. В ней необходимо иметь 64 усилителя считывания, и два шестиразрядных регистра для хранения кода адреса, дешифраторы строк столбцов с 64 выходами каждый, устройство ввода-вывода и устройство управления и синхронизации, которое будет формировать управляющие сигналы. Элементом память в данном случае будет конденсатор, который с помощью ключевой схемы на транзисторе будет подключаться к разрядной шине. При совпадении выходного сигнала дешифратора столбца и управляющего сигнала F3 открываются ключи выборки столбцов, шины ввода-вывода соединяются с выбранной разрядной шиной – производится считывание или запись информации.

Микросхема управляется четырьмя сигналами: кодом адреса, тактовым сигналом, выборки микросхемы и записи-считывания.

Сигналы адреса (выборка элементов памяти_ поступают на регистры строк и столбцов для выбора элемента памяти. Обращение к матрице по адресным входам разрешается тактовым сигналом. Код адреса после записи в регистрах дешифруется. Одновременно запускаются формирователи F1 и через него - F2, управляющие выбором строки. Также от F1 селектором строк разрядные шины подключается к конденсаторам опорных элементов. Из-за того, что собственная емкость шин больше, чем емкость запоминающего конденсатора, разность потенциалов между ними при их подключении друг к другу будет незначительна. Поэтому необходим весьма чувствительный усилитель считывания.

Сигнал F2 включает усилитель считывания и происходит регенерация информации во всех элементах памяти выбранной строки.

По сигналу ВМС запускается формирователь F3 и через него F4, которые коммутируют цеп вывода информации и шины ввода-вывода с разрядной шиной через транзисторные ключи. Информация считывается. С окончанием тактового сигнала все узлы микросхемы возвращаются в исходное состояние.

Поскольку динамической памяти необходима регенерация, число циклов которой будет равно число строк в матрице. Этот цикл идет когда нет разрешающего сигнала ВМС. Для этого цикла необходимы счетчик, коммутатор, триггер и генератор регенерации, синхронизированный тактовым сигналом.

Реферат опубликован: 18/10/2007